Date: - 31 Jan, 2008

Data Sheet Issue:- 1

# **Provisional Data**

# **Anode Shorted Gate Turn-Off Thyristor** Types G1000QC400 to G1000QC450

### **Absolute Maximum Ratings**

|                      | VOLTAGE RATINGS                                 | MAXIMUM<br>LIMITS | UNITS |

|----------------------|-------------------------------------------------|-------------------|-------|

| $V_{DRM}$            | Repetitive peak off-state voltage, (note 1)     | 4500              | V     |

| $V_{RSM}$            | Non-repetitive peak off-state voltage, (note 1) | <b>/</b> 4500     | V     |

| $V_{\text{DC-link}}$ | Maximum continuos DC-link voltage               | 2800              | V     |

| $V_{RRM}$            | Repetitive peak reverse voltage                 | 18                | V     |

| $V_{RSM}$            | Non-repetitive peak reverse voltage             | 18                | V     |

|                     | RATINGS                                                               | MAXIMUM<br>LIMITS      | UNITS            |

|---------------------|-----------------------------------------------------------------------|------------------------|------------------|

| $I_{TGQ}$           | Peak turn-off current, (note 2)                                       | 1000                   | Α                |

| Ls                  | Snubber loop inductance, I <sub>TM</sub> =I <sub>TGQ</sub> , (note 2) | 300                    | nH               |

| $I_{T(AV)M}$        | Mean on-state current, T <sub>sink</sub> =55°C (note 3)               | 443                    | Α                |

| I <sub>T(RMS)</sub> | Nominal RMS on-state current, 25°C (note 3)                           | 867                    | Α                |

| I <sub>TSM</sub>    | Peak non-repetitive surge current to=10ms, (Note 4)                   | 6500                   | Α                |

| I <sub>TSM2</sub>   | Peak non-repetitive surge current (=2ms, (Note 4)                     | 11450                  | kA               |

| l <sup>2</sup> t    | I <sup>2</sup> t capacity for fusing t <sub>p</sub> =10ms             | 211.25×10 <sup>3</sup> | A <sup>2</sup> s |

| di/dt <sub>cr</sub> | Critical rate of rise of op-state current, (note 5)                   | 300                    | A/µs             |

| P <sub>FGM</sub>    | Peak forward gate power                                               | 185                    | W                |

| $P_{RGM}$           | Peak reverse gate power                                               | 7                      | kW               |

| I <sub>FGM</sub>    | Peak forward gate current ( )                                         | 100A                   | Α                |

| $V_{RGM}$           | Peak reverse gate voltage (note 6)                                    | 18                     | V                |

| t <sub>off</sub>    | Minimum permissible off-time (note 2)                                 | 80                     | μs               |

| t <sub>on</sub>     | Minimum permissible on-time                                           | 20                     | μs               |

| T <sub>j op</sub>   | Operating temperature range                                           | -40 to +125            | °C               |

| $T_{stg}$           | Storage temperature range                                             | -40 to +125            | °C               |

1) V<sub>GK</sub>=-2Volts.

(2)  $T_1$ =125°C,  $V_D$ =2806V,  $V_{DM} \le 4500$ V di<sub>GQ</sub>/dt=25A/ $\mu$ s,  $I_{TGQ}$ =1000A and  $C_S$ =1 $\mu$ F.

3) Double-side cooled, single phase; 50Hz, 180° half-sinewave.

(4) Tjinittat)=125°C, single phase, 180° sinewave, re-applied voltage V<sub>D</sub>=V<sub>R</sub>≤10V.

5) For di/dt>300A/µs please consult the factory.

6) May exceed this value during turn-off avalanche period.

# **Characteristics**

|                     | Parameter                                  | MIN  | TYP  | MAX        | TEST CONDITIONS                                                                                                | UNITS |

|---------------------|--------------------------------------------|------|------|------------|----------------------------------------------------------------------------------------------------------------|-------|

| V <sub>TM</sub>     | Maximum peak on-state voltage              | -    | 3.75 | 4.0        | I <sub>G</sub> =2A, I <sub>T</sub> =1000A                                                                      | V     |

| IL                  | Latching current                           | -    | 10   | -          | T <sub>j</sub> =25°C                                                                                           | Α     |

| I <sub>H</sub>      | Holding current.                           | -    | 10   | -          | T <sub>j</sub> =25°C                                                                                           | Α     |

| dv/dt <sub>cr</sub> | Critical rate of rise of off-state voltage | 1000 | -    | -          | V <sub>D</sub> =2800V, V <sub>GR</sub> =-2V                                                                    | V/µs  |

| I <sub>DRM</sub>    | Peak off state current                     | -    | -    | 50         | Rated V <sub>DRM</sub> , V <sub>GR</sub> =-2V                                                                  | mA    |

| I <sub>RRM</sub>    | Peak reverse current                       | -    | -    | 60         | V <sub>RR</sub> =16V                                                                                           | mA    |

| $I_{GKM}$           | Peak negative gate leakage current         | -    | -    | 60         | V <sub>GR</sub> =-16V                                                                                          | mA    |

|                     |                                            | -    | 1.0  | -          | T <sub>j</sub> =-40°C                                                                                          | V     |

| $V_{GT}$            | Gate trigger voltage                       | -    | 0.8  | - <        | $T_{\rm j}$ =25°C $V_{\rm D}$ =25V, $R_{\rm L}$ =25m $\Omega$                                                  | V     |

|                     |                                            | -    | 0.6  | -          | T <sub>j</sub> =125°C                                                                                          | V     |

|                     |                                            | -    | 2    | 3.5        | T <sub>j</sub> =-40°C                                                                                          | Α     |

| $I_{GT}$            | Gate trigger current                       | -    | 0.8  | 1.5        | $T_{j}=25^{\circ}C$ $V_{D}=25V$ , $R_{L}=25m\Omega$                                                            | Α     |

|                     |                                            | -    | 0.2  | 0.4        | T <sub>j</sub> =125°C                                                                                          | Α     |

| t <sub>d</sub>      | Delay time                                 | -    | 0.1  | ( - (      | V <sub>D</sub> =2800V <sub>λ</sub> I <sub>TGQ</sub> =1000A, di <sub>T</sub> /dt=300A/μs, I <sub>GM</sub> =20A, | μs    |

| t <sub>gt</sub>     | Turn-on time                               | -    | 3.0  | 6.0        | dig/dt=20A/µs                                                                                                  | μs    |

| t <sub>f</sub>      | Fall time                                  | -    | 1.2  | / -        |                                                                                                                | μs    |

| $t_{gq}$            | Turn-off time                              | -    | 13(  | 16<        |                                                                                                                | μs    |

| $I_{GQ}$            | Peak turn-off gate current                 | -    | 275  |            | V <sub>D</sub> =2800V, I <sub>TGQ</sub> =1000A, di <sub>GQ</sub> /dt=25A/µs, V <sub>GR</sub> =-16V,            | Α     |

| $Q_GQ$              | Turn-off gate charge                       | (-   | 1.8  | 3.0        | Ć <sub>s</sub> =1μF                                                                                            | mC    |

| t <sub>tail</sub>   | Tail time                                  | 7-(  | 35   | 50         |                                                                                                                | μs    |

| t <sub>gw</sub>     | Gate off-time (note 3)                     | 100  | -    | <b>√</b> - |                                                                                                                | μs    |

|                     |                                            |      | ->   | 0.038      | Double side cooled                                                                                             | K/W   |

| $R_{\text{thJK}}$   | Thermal resistance junction to sink        |      |      | 0.061      | Cathode side cooled                                                                                            | K/W   |

|                     | $\wedge \vee /$                            | (-)  | /-   | 0.101      | Anode side cooled                                                                                              | K/W   |

| F                   | Mounting force                             | 13   | _    | 17         | (see note 2)                                                                                                   | kN    |

| $W_t$               | Weight                                     | -    | 325  | -          |                                                                                                                | g     |

### Notes:-

- Unless otherwise indicated T<sub>j</sub>=125°C.

For other clamping forces, consult factory.

The gate off-time, is the period during which the gate circuit is required to remain at low impedance to allow for the passage of tail current.

#### Notes on ratings and characteristics.

#### 1. Maximum Ratings.

#### 1.1 Off-state voltage ratings.

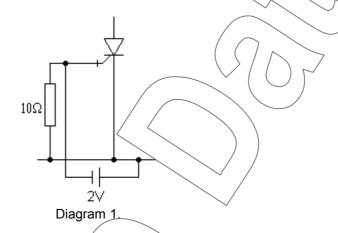

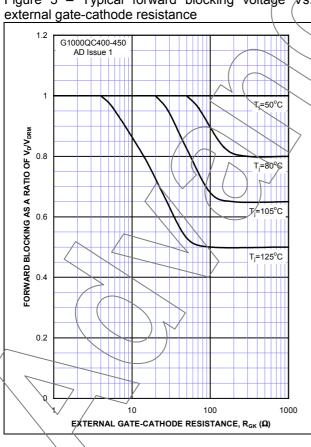

Unless otherwise indicated, all off-state voltage ratings are given for gate conditions as diagram 1. For other gate conditions see the curves of figure 5. It should be noted that  $V_{DRM}$  is the repeatable peak voltage which may be applied to the device and does not relate to a DC operating condition.

# 1.2 Reverse voltage rating.

All devices in this series have a minimum V<sub>RRM</sub> of 18 Volts.

#### 1.3 Peak turn-off current.

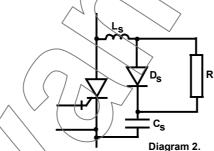

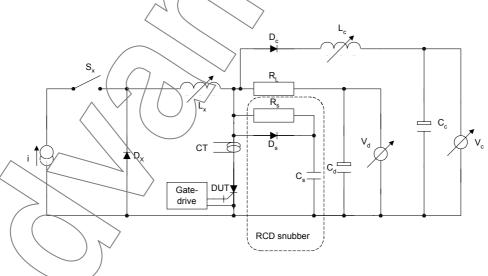

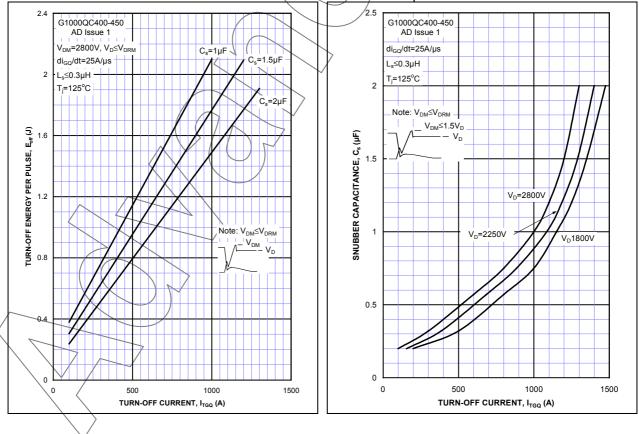

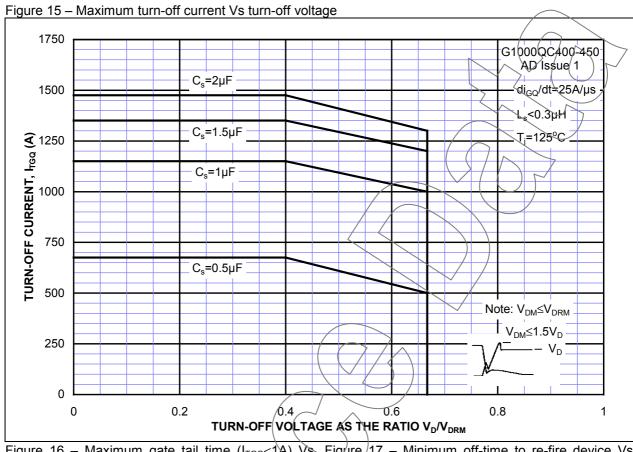

The figure given in maximum ratings is the highest value for normal operation of the device under conditions given in note 2 of ratings. For other combinations of  $I_{TGQ}$ ,  $V_D$  and  $C_s$  see the curves in figures 14 & 15. The curves are effective over the normal operating range of the device and assume a snubber circuit equivalent to that given in diagram 2. If a more complex snubber, such as an Underland circuit, is employed then the equivalent  $C_S$  should be used and  $L_s < 0.3 \mu H$  must be ensured for the curves to be applied.

#### 1.4 R.M.S and average current.

Measured as for standard thyristor conditions, double side cooled, single phase, 50Hz, 180° half-sinewave. These are included as a guide to compare the alternative types of GTO thyristors available, values can not be applied to practical applications, as they do not include switching losses.

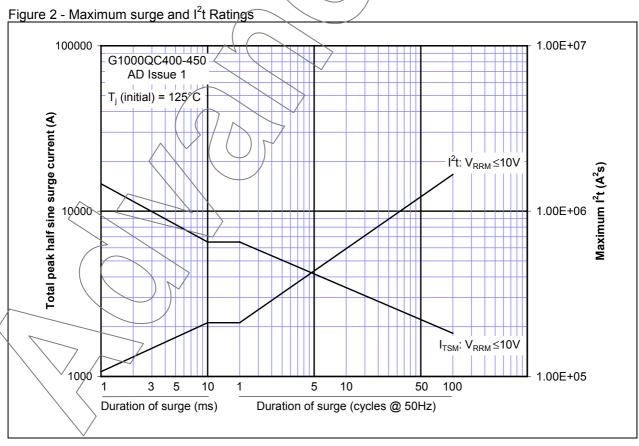

# 1.5 Surge rating and I2t.

Ratings are for half-sinewave, peak value against duration is given in the curve of figure 2.

#### 1.6 Snubber loop inductance.

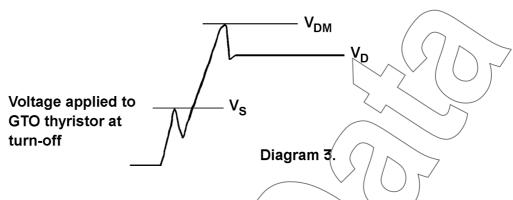

Use of GTO thyristors with snubber loop inductance,  $L_s$ <0.3 $\mu$ H implies no dangerous  $V_s$  voltages (see diagrams 2 &/3) can be applied, provided the other conditions given in note 1.3 are enforced. Alternatively  $V_s$  should be limited to 800 Volts to avoid possible device failure.

#### 1.7 Critical rate of rise of on-state current

The value given is the maximum repetitive rating, but does not imply any specific operating condition. The high turn-on losses associated with limit di/dt would not allow for practical duty cycle at this maximum condition. For special pulse applications, such as crowbars and pulse power supplies, a much higher di/dt is possible. Where the device is required to operate with infrequent high current pulses, with natural commutation (i.e. not gate turn-off), then di/dt>5kA/µs is possible. For this type of operation individual specific evaluation is required.

#### 1.8 Gate ratings

The absolute conditions above which the gate may be damaged it is permitted to allow V<sub>GK(AV)</sub> during turnoff to exceed V<sub>RGM</sub> which is the implied DC condition.

#### 1.9 Minimum permissible off time.

This time relates specifically to re-firing of device (see also note on gate-off time 2.7). The value given in the ratings applies only to operating conditions of ratings note 2.

#### 1.10 Minimum permissible on-time.

Figure is given for minimum time to allow complete conduction of all the GTO thyristor islands. Where a simple snubber, of the form given in diagram 1. (or any other non-energy recovery type which discharges through the GTO at turn-on) the actual minimum on-time will usually be fixed by the snubber circuit time constant, which must be allowed to fully discharge before the GTO thyristor is turned off. If the anode circuit has di/dt<10A/µs then the minimum on time should be increased, the actual value will depend upon the di/dt and operating conditions (each case needs to be assessed on an individual basis).

#### 2 Characteristics

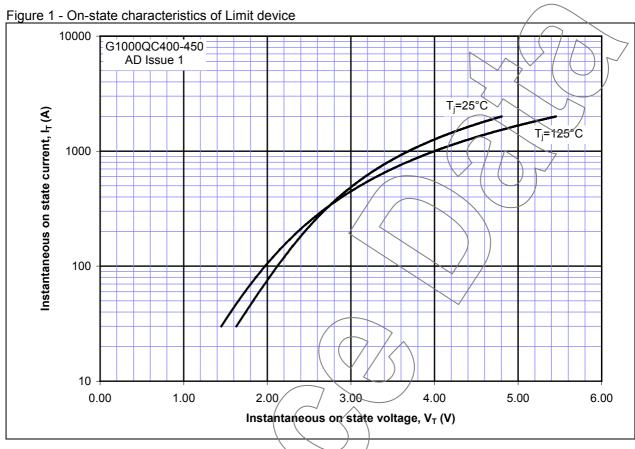

# 2.1 Instantaneous on-state voltage

Measured using a 500µs square pulse, see also the curves of figure 1 for other values of l<sub>™</sub>.

#### 2.2 Latching and holding current

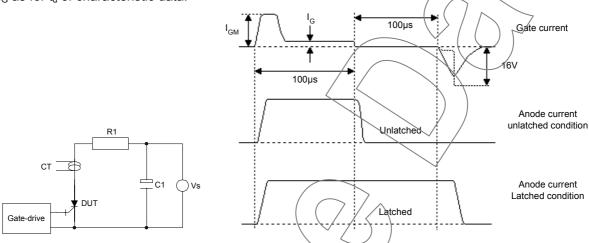

These are considered to be approximately equal and only the latching current is measured, type test only as outlined below. The test circuit and wave diagrams are given in diagram 4. The anode current is monitored on an oscilloscope while V<sub>D</sub> is increased, until the current is seen to flow during the un-gated period between the end of I<sub>G</sub> and the application of reverse gate voltage. Test/frequency is 100Hz with I<sub>GM</sub> & I<sub>G</sub> as for t<sub>d</sub> of characteristic data.

Diagram 4, Latching test circuit and waveforms.

#### 2.3 Critical dv/dt

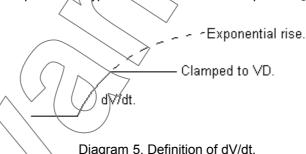

The gate conditions are the same as for 1.1, this characteristic is for off-state only and does not relate to dv/dt at turn-off. The measurement, type test only, is conducted using the exponential ramp method as shown in diagram 5. It should be noted that GTQ thyristors have a poor static dv/dt capability if the gate is open circuit or R<sub>GK</sub> is high impedance. Typical values: - dv/dt<100V/μs for R<sub>GK</sub>>10Ω.

2.4 Off-state leakage.

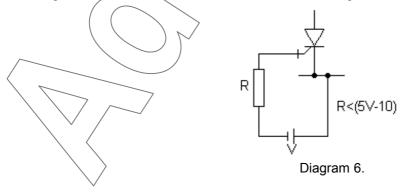

For I<sub>DRM</sub> & I<sub>RRM</sub> see notes 1.1 & 1.2 for gate leakage I<sub>GK</sub>, the off-state gate circuit is required to sink this leakage and still maintain minimum of -2 Volts. See diagram 6.

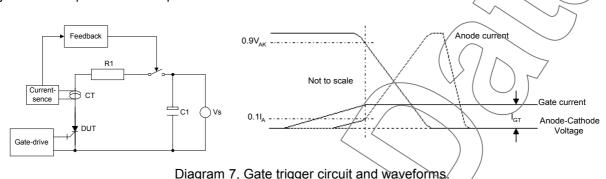

#### 2.5 Gate trigger characteristics.

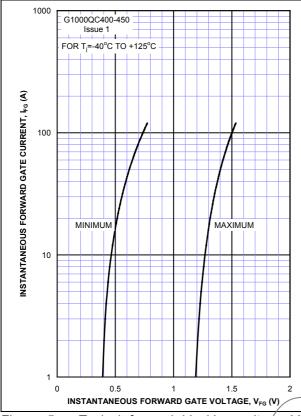

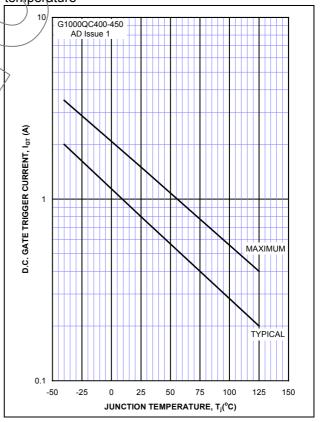

These are measured by slowly ramping up the gate current and monitoring the transition of anode current and voltage (see diagram 7). Maximum and typical data of gate trigger current, for the full junction temperature range, is given in the curves of figure 6. Only typical figures are given for gate trigger voltage, however, the curves of figure 3 give the range of gate forward characteristics, for the full allowable junction temperature range. The curves of figures 3 & 6 should be used in conjunction, when considering forward gate drive circuit requirement. The gate drive requirements should always be calculated for lowest junction temperature start-up condition.

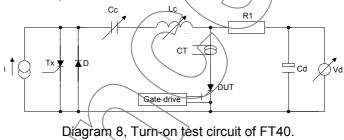

2.6 Turn-on characteristics

The basic circuit used for turn-on tests is given in diagram 8. The test is initiated by establishing a circulating current in Tx, resulting in VD appearing across Cc/Lc. When the test device is fired Cc/Lc discharges through DUT and commutates T<sub>x</sub> off, as pulse from C<sub>c</sub>/L<sub>c</sub> decays the constant current source continues to supply a fixed current to DUT. Changing value of Cc & Lc allows adjustment of I<sub>TM</sub> and di/dt respectively, V<sub>D</sub> and i are also adjustable.

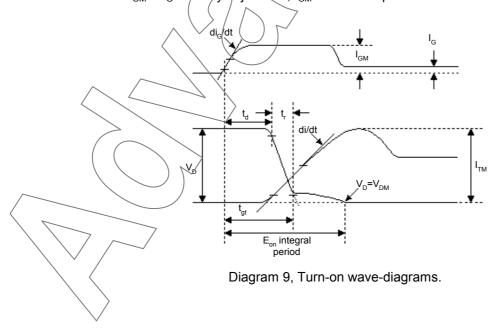

The definitions of turn-on parameters used in the characteristic data are given in diagram 9. The gate circuit conditions I<sub>GM</sub> & I<sub>G</sub> are fully adjustable, I<sub>GM</sub> duration 10µs.

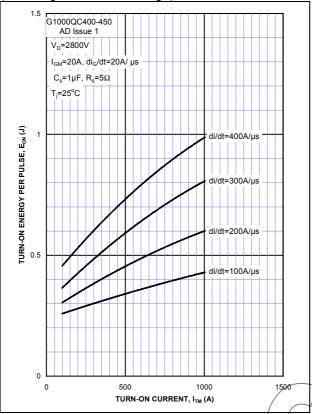

In addition to the turn-on time figures given in the characteristics data, the curves of figure 8 give the relationship of tot to di/dt and I<sub>GM</sub>. The data in the curves of figure 7, gives the turn-on losses with a snubber of the form given in diagram 2. Only typical losses are given due to the large number of variables which effect E<sub>on</sub>. It is unlikely that all negative aspects would appear in any one application, so typical figures can be considered as worst case. Where the turn-on loss is higher than the figure given it will in most cases be compensated by reduced turn-off losses, as variations in processing inversely effect many parameters. For a worst case device, which would also have the lowest turn-off losses, Eon would be 1.5x values given in the curves of figure 7. Turn-on losses are measured over the integral period specified below:-

$$Eon = \int_{0}^{10\mu s} iv.dt$$

The turn-on loss can be sub-divided into two component parts, firstly that associated with tot and secondly the contribution of the voltage tail. For this series of devices to contributes 40% and the voltage tail 60% (These figures are approximate and are influenced by several second order effects). The loss during tot is greatly affected by gate current and as with turn-on time (figure 8), it can be reduced by increasing  $I_{GM}$ . The turn-on loss associated with the voltage tail is not effected by the gate conditions and can only be reduced by limiting di/dt, where appropriate a turn-on snubber should be used. In applications where the snubber is discharged through the GTO thyristor at turn-on, selection of discharge resistor will effect E<sub>on</sub>. The curves of figure 8 are given for a snubber as shown in diagram 2, with R=5 $\Omega$ , this is the lowest recommended value giving the highest Eon, higher values will reduce Eon.

#### 2.7 Turn-off characteristics

The basic circuit used for the turn-off test is given in diagram 10. Prior to the negative gate pulse being applied constant current, equivalent to  $I_{TGO}$ , is established in the DUT. The switch  $S_x$  is opened just before DUT is gated off with a reverse gate pulse as specified in the characteristic/data curves. After the period  $t_{\text{at}}$  voltage rises across the DUT, dv/dt being/limited by the snubber circuit. Voltage will continue to rise across DUT until D<sub>c</sub> turns-on at a voltage set by the active clamp C<sub>c</sub>, the voltage will be held at this value until energy stored in  $L_x$  is depleted, after which it will fall to  $V_{DC}$ . The value of  $L_x$  is selected to give required  $V_D$  Over the full tail time period. The overshoot voltage  $V_{DM}$  is derived from  $L_c$  and forward voltage characteristic of  $D_C$ , typically  $V_{DM}$ =1.2 $V_D$  to 1.5 $V_D$  depending on test settings. The gate is held reverse biased through a low impedance circuit until the tail current is fully extinguished.

Diagram 10, Turn-off test circuit.

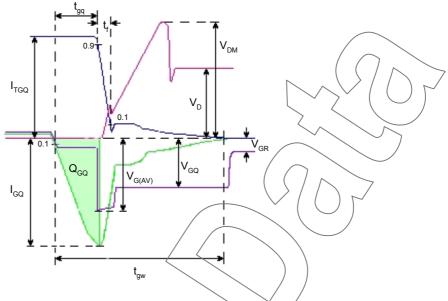

The definitions of turn-off parameters used in the characteristic data are given in diagram 11.

Diagram 11, Turn-off parameter definitions.

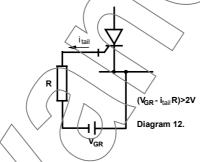

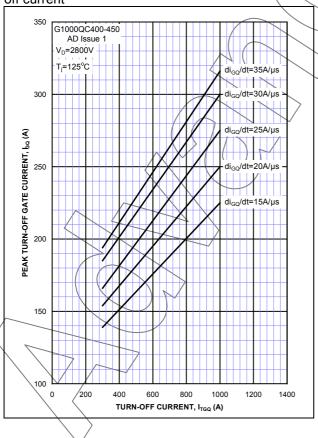

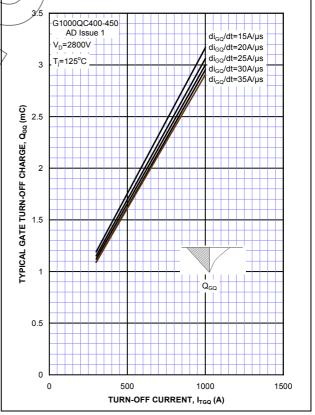

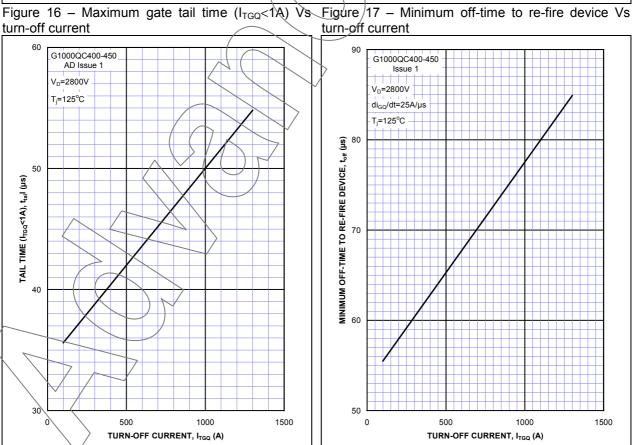

In addition to the turn-off figures given in characteristic data, the curves of figures 9, 10 & 11 give the relationship of  $I_{GQ}$  Q<sub>GQ</sub> and  $t_{gq}$  to turn-off current ( $I_{TGQ}$ ) and di<sub>GQ</sub>/dt. Only typical values of  $I_{GQ}$  are given due to a great dependence upon the gate circuit impedance, which is a function of gate drive design not the device. The  $t_{gq}$  is also, to a lesser extent, affected by circuit impedance and as such the maximum figures given in data assume a good low impedance circuit design. The curves of figures 16 & 17 give the tail time and minimum off time to re-fire device as a function of turn-off current. The minimum off time to re-fire the device is distinct from  $t_{gw}$ , the gate off time given in characteristics. The GTO thyristor may be safely re-triggered when a small amount of tail current is still flowing. In contrast, the gate circuit must remain low impedance until the tail current has fallen to zero or below a level which the higher impedance  $V_{GR}$  circuit can sink without being pulled down below -2 Volts. If the gate circuit is to be switched to a higher impedance before the tail current has reached zero then the requirements of diagram 12 must be applied.

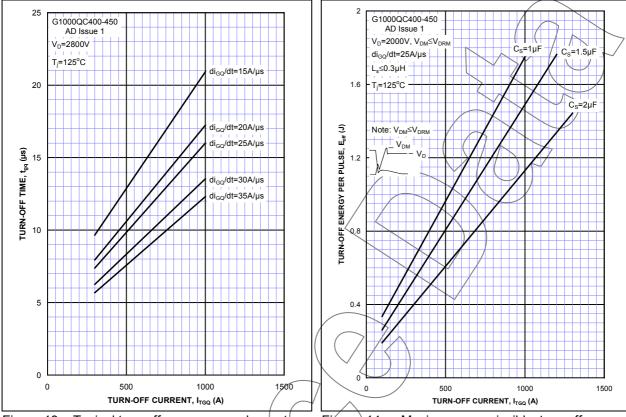

The figure  $t_{gw}$ , as given in the characteristic data, is the maximum time required for the tail current to decay to zero. The figure is applicable under all normal operating conditions for the device; provided suitable gate drive is employed. At lower turn-off current, or with special gate drive considerations, this time may be reduced (each case needs to be considered individually). Typical turn-off losses are given in the curves of figures 12 & 13, the integration period for the losses is nominally taken to the end of the tail time ( $l_{tail}$ <1A) i.e.:-

$$Eoff = \int_{0}^{tgt+ttail} iv.dt$$

The curves of figure 12 give the turn-off energy for a fixed  $V_D$  with a  $V_{DM} \le V_{DRM}$ , whereas the curves of figure 13 give the turn-off energy with a fixed value of  $V_{DM}$  and  $V_{D} \le V_{DC-link}$ . The curves are for energy against turn-off current/snubber capacitance (snubber equivalent to diagram 2 is assumed). From these curves a typical value of turn-off energy for any combination of I<sub>TGQ</sub>/C<sub>s</sub> can be derived. Only typical data is included, to allow for the trade-off with on-state voltage (V<sub>TM</sub>) which is a feature of these/devices, see diagram 13. When calculating losses in an application, the use of a maximum  $V_{TM}$  and typical  $E_{off}$  will (under normal operating frequencies) give a more realistic value. The lowest V<sub>TM</sub> device of this type would have a maximum turn-off energy of 1.5x the figure given in the curves of figures 12 & 13/

#### 2.8 Safe turn-off periphery

The necessity to control dv/dt at tun-off for the GTO thyristor implies a trade-off between I<sub>TGO</sub>/V<sub>DM</sub>/C<sub>s</sub>. This information is given in the curves of figures 14 & 15. The information in these curves should be considered as maximum limits and not implied operating conditions, some margin of 'safety' is advised with the conditions of the curves reserved for occasional excursions/ It should be noted that these curves are derived at maximum junction temperature, however, they may be applied across the full operating temperature range of the device provided additional precautions are taken. At very low temperature, (below -10°C) the fall-time of device becomes very rapid and can give rise to very high turn-off voltage spikes, as such it is advisable to reduce snubber loop inductance to <0.2µH to minimise this effect.

# **Curves**

Figure 3 – Forward gate characteristics

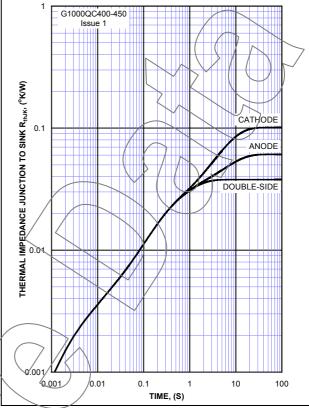

Figure 4 – Transient thermal impedance

Figure 5 - Typical forward blocking voltage

√s. Figure 6 - Gate trigger current Vs junction temperature

Figure 7 - Typical turn-on energy per pulse Figure 8 - Maximum turn-on time Vs rate of rise of (including snubber discharge) on-state current

I<sub>GM</sub>=10A G1000QC400-450 AD Issue 1  $V_D = 2800V, I_{TM} = 1000A$ I<sub>GM</sub>=20A  $t_r$  of  $I_{GM} \le 2\mu s$ T<sub>j</sub>=25°C I<sub>GM</sub>=40A TURN-ON TIME, t<sub>gt</sub> (µs) 2 100 RATE OF RISE OF ON-STATE CURRENT, di/dt (A/ μs)

Figure 9 Typical peak turn-off gate current Vs turn-Figure 10 - Maximum gate turn-off charge Vs turnoff current off current

Figure 11 - Maximum turn-off time Vs turn-off Figure 12 - Typical turn-off energy per pulse Vs turn-off current current

Figure 13 – Typical turn-off energy per pulse vs turn-Figure 14 - Maximum permissible turn-off current off current Vs snubber capacitance

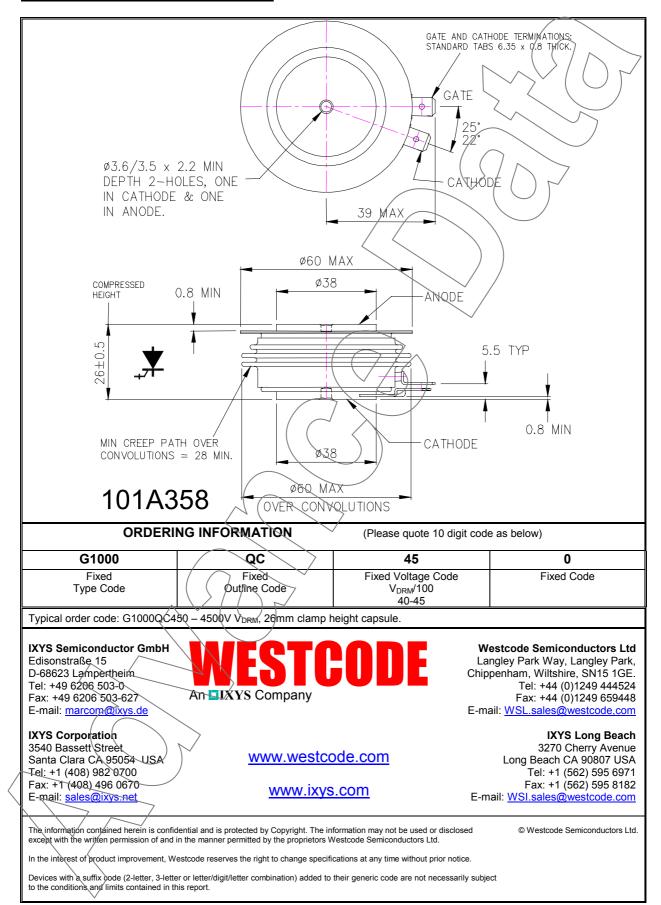

#### **Outline Drawing & Ordering Information**