### Designer's Data Sheet

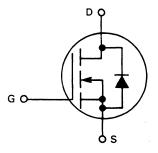

## N-CHANNEL ENHANCEMENT MODE SILICON GATE TMOS POWER FIELD EFFECT TRANSISTOR

These TMOS Power FETs are designed for 120 V line operated high speed power switching applications such as motor controls, switching regulators, converters, solenoid and relay drivers.

- Silicon Gate for Fast Switching Speeds Switching Times Specified at 100°C

- Designers Data IDSS, VDS(on), VGS(th) and SOA Specified at Elevated Temperature

- Rugged SOA is Power Dissipation Limited

- Source to Drain Diode Characterized for Use With Inductive Loads

#### **MAXIMUM RATINGS**

| Rating                                                            | Symbol                            | MTM10N25<br>MTP10N25 | Unit          |

|-------------------------------------------------------------------|-----------------------------------|----------------------|---------------|

| Drain — Source Voltage                                            | V <sub>DSS</sub>                  | 250                  | Vdc           |

| Drain — Gate Voltage (RGS = 1.0 M $\Omega$ )                      | V <sub>DGR</sub>                  | 250                  | Vdc           |

| Gate — Source Voltage                                             | VGS                               | ±20                  | Vdc           |

| Drain Current<br>Continuous<br>Pulsed                             | I <sub>D</sub>                    | 10<br>30             | Adc           |

| Gate Current — Pulsed                                             | IGM                               | 1.5                  | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                                | 100<br>0.8           | Watts<br>W/°C |

| Operating and Storage<br>Temperature Range                        | T <sub>J</sub> , T <sub>Stg</sub> | -65 to 150           | °C            |

#### THERMAL CHARACTERISTICS

| Thermal Resistance Junction to Case                                           | R <sub>θ</sub> JC | 1.25 | °C/W |

|-------------------------------------------------------------------------------|-------------------|------|------|

| Maximum Lead Temp. for<br>Soldering Purposes, 1/8"<br>from case for 5 seconds | TL                | 275  | °C   |

#### Designer's Data for "Worst Case" Conditions

The Designer's Data Sheet permits the design of most circuits entirely from the information presented. Limit curves—representing boundaries on device characteristics—are given to facilitate "worst case" design.

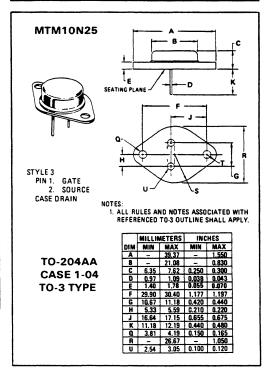

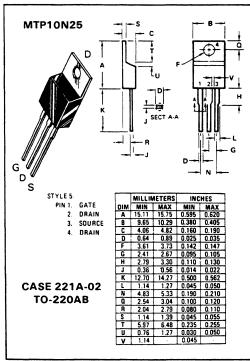

## MTM10N25 MTP10N25

#### 10 AMPERE

#### N-CHANNEL TMOS POWER FET

r<sub>DS(on)</sub> = 0.45 OHM 250 VOLTS

| Characteristic                                                                                                                                                |                                                            | Symbol               | Min           | Max                  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|---------------|----------------------|------|

| OFF CHARACTERISTICS                                                                                                                                           |                                                            |                      |               |                      |      |

| Drain-Source Breakdown Voltage<br>(V <sub>GS</sub> = 0, I <sub>D</sub> = 5.0 mA)                                                                              | MTM10N25/MTP10N25                                          | V <sub>(BR)DSS</sub> | 250           | _                    | Vdc  |

| Zero Gate Voltage Drain Current (VDS = 0.85 Rated VDSS, VGS = 0) T = 100°C                                                                                    |                                                            | IDSS                 |               | 0.25<br>2.5          | mAdc |

| Gate-Body Leakage Current<br>(VGS = 20 Vdc, VDS = 0)                                                                                                          |                                                            | IGSS                 | -             | 500                  | nAdc |

| ON CHARACTERISTICS*                                                                                                                                           |                                                            |                      |               |                      |      |

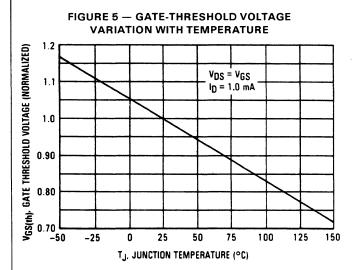

| Gate Threshold Voltage<br>(I <sub>D</sub> = 1.0 mA, V <sub>DS</sub> = V <sub>GS</sub> )<br>T <sub>J</sub> = 100°C                                             |                                                            | VGS(th)              | 2.0<br>1.5    | 4.5<br>4.0           | Vdc  |

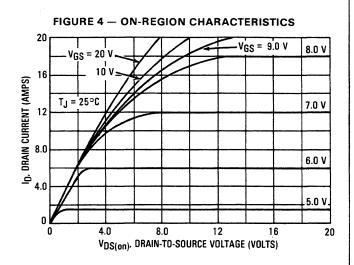

| Drain-Source On-Voltage (V <sub>GS</sub> = 1<br>(I <sub>D</sub> = 5.0 Adc)<br>(I <sub>D</sub> = 10 Adc)<br>(I <sub>D</sub> = 5.0 Adc, T <sub>J</sub> = 100°C) | IO V)                                                      | V <sub>DS(on)</sub>  | = =           | 2.25<br>5.60<br>4.50 | Vdc  |

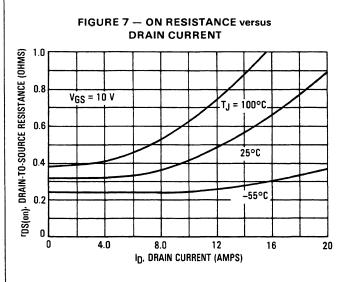

| Static Drain-Source On-Resistance<br>(VGS = 10 Vdc, I <sub>D</sub> = 5.0 Adc)                                                                                 |                                                            | <sup>r</sup> DS(on)  | _             | 0.45                 | Ohms |

| Forward Transconductance<br>(V <sub>DS</sub> = 15 V, I <sub>D</sub> = 5.0 A)                                                                                  |                                                            | 9fs                  | 3.0           | -                    | mhos |

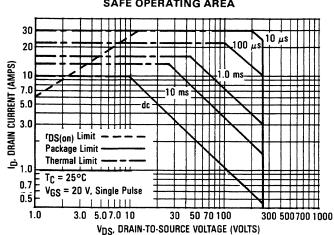

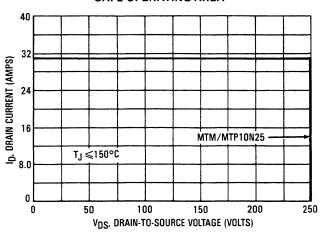

| SAFE OPERATING AREAS                                                                                                                                          |                                                            |                      |               |                      |      |

| Forward Biased Safe Operating Area                                                                                                                            |                                                            | FBSOA                | See Figure 9  |                      |      |

| Switching Safe Operating Area                                                                                                                                 |                                                            | SSOA                 | See Figure 10 |                      |      |

| DYNAMIC CHARACTERISTICS                                                                                                                                       |                                                            |                      |               |                      |      |

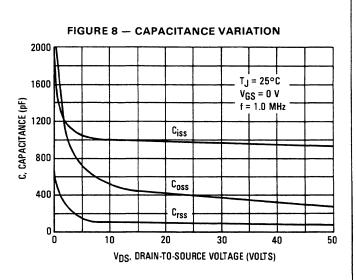

| Input Capacitance                                                                                                                                             |                                                            | C <sub>iss</sub>     | _             | 1200                 | pF   |

| Output Capacitance                                                                                                                                            | (V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1.0 MHz) | Coss                 | _             | 600                  | pF   |

| Reverse Transfer Capacitance                                                                                                                                  |                                                            | C <sub>rss</sub>     | _             | 150                  | pF   |

| SWITCHING | CHAR | ACTERISTIC | S* (Tj = | : 100°C) |

|-----------|------|------------|----------|----------|

|-----------|------|------------|----------|----------|

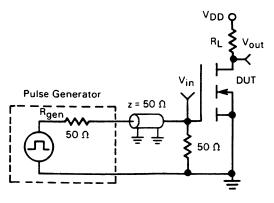

| Turn-On Delay Time  |                                                 | t <sub>d(on)</sub> |   | 50  | ns |

|---------------------|-------------------------------------------------|--------------------|---|-----|----|

| Rise Time           | $(V_{DS} = 25 \text{ V, } I_D = 5.0 \text{ A,}$ | t <sub>r</sub>     | _ | 250 | ns |

| Turn-Off Delay Time | R <sub>gen</sub> = 50 ohms)                     | td(off)            |   | 100 | ns |

| Fall Time           | See Figures 1 and 2.                            | tf                 | _ | 120 | ns |

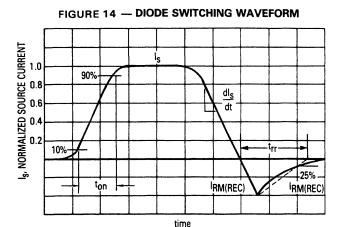

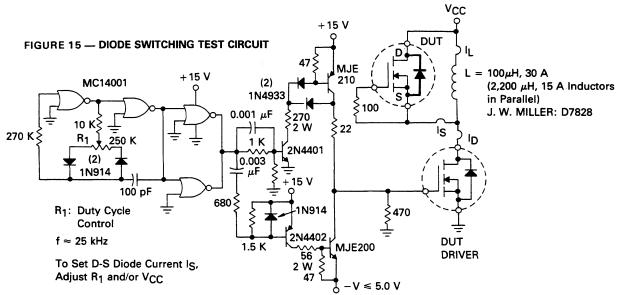

#### **SOURCE DRAIN DIODE CHARACTERISTICS\***

| Characteristic        |                        | Symbol          | Тур | Unit |

|-----------------------|------------------------|-----------------|-----|------|

| Forward On-Voltage    | I <sub>S</sub> = 10 A  | V <sub>SD</sub> | 1.5 | Vdc  |

| Forward Turn-On Time  | V <sub>GS</sub> = 0    | ton             | 50  | ns   |

| Reverse Recovery Time | See Figures 14 and 15. | t <sub>rr</sub> | 300 | ns   |

<sup>\*</sup>Pulse Test: Pulse Width  $\leq$ 300  $\mu$ s, Duty Cycle  $\leq$ 2%.

#### **RESISTIVE SWITCHING**

FIGURE 1 — SWITCHING TEST CIRCUIT

# FIGURE 2 — SWITCHING WAVEFORMS

#### **THERMAL RESPONSE**

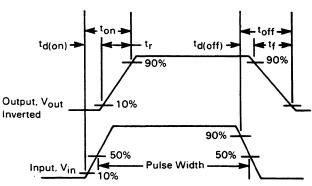

#### FIGURE 11 — MTM10N25

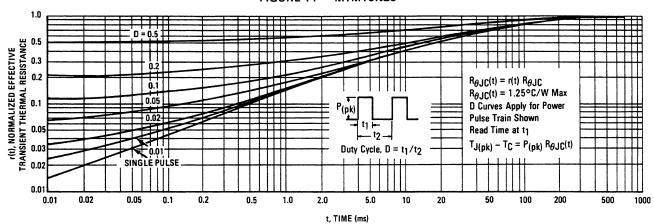

#### FIGURE 12 - MTP10N25

#### TMOS POWER FET CONSIDERATIONS

**Switching Speed** — The switching speeds of these devices are dependent on the driving impedance. Extremely fast switching speeds can be attained by driving the gate from a voltage source.

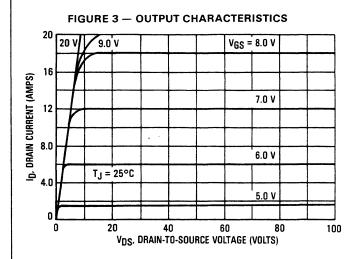

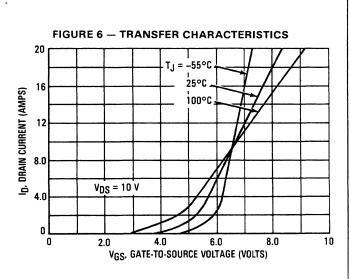

**Transfer Characteristics** — The transfer characteristics are linear at drain currents of 2.0 Amps. (See Figure 6.) Linear amplifiers with high frequency response can be designed using this product.

Gate Voltage Rating — Never exceed the gate voltage rating of  $\pm 20$  V. Exceeding the rated VGS can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gate of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the

devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate to source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

Handling and Packaging — MOS ICs are susceptible to damage from electrostatic charge. Experience has shown that these devices are more rugged than MOS ICs. This is primarily due to the comparatively larger capacitances associated with power devices, however, reasonable precautions in handling and packaging MOS devices should be observed.

**MOTOROLA** Semiconductor Products Inc. -

#### SAFE OPERATING AREA INFORMATION

FIGURE 9 — MAXIMUM RATED SWITCHING SAFE OPERATING AREA

FIGURE 10 — MAXIMUM RATED SWITCHING SAFE OPERATING AREA

#### FORWARD BIASED SAFE OPERATING AREA

The dc data of Figure 9 is based on a case temperature ( $T_C$ ) of 25°C and a maximum junction temperature ( $T_{Jmax}$ ) of 150°. The actual junction temperature depends on the power dissipated in the device and its case temperature. For various pulse widths, duty cycles, and case temperatures, the peak allowable drain current ( $I_{DM}$ ) may be calculated with the aid of the following equation:

$$I_{DM} = I_{D}(25^{\circ}C) \left[ \frac{T_{J(max)} - T_{C}}{P_{D} \cdot R_{\theta}JC \cdot r(t)} \right]$$

where

$I_D(25^{\circ}C)$  = the dc drain current at  $T_C = 25^{\circ}C$  from Figure 9.

$T_{J(max)}$  = rated maximum junction temperature.

T<sub>C</sub> = device case temperature.

$P_D$  = rated power dissipation at  $T_C$  = 25°C.  $R_{\theta JC}$  = rated steady state thermal resistance

r(t) = normalized thermal response from Figures 11

and 12.

#### **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 10, is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current,  $I_{DM}$  and the breakdown voltage,  $V_{(BR)DSS}$ . The switching SOA shown in Figure 10 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

The power averaged over a complete switching cycle must be less than:

#### TYPICAL CHARACTERISTICS

#### TMOS SOURCE TO DRAIN DIODE CHARACTERISTICS

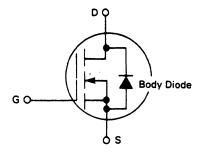

In the fabrication of a TMOS FET, a diode is formed across the source-to-drain terminals as shown in Figure 13. Reversal of the drain voltage will cause current flow in the reverse direction. This

diode is formed across the higher 13. Reversal of the diodes, therefore, typical characteristics of the on voltage, forward turn-on and reverse recovery times are given.

FIGURE 13 — TMOS FET WITH SOURCE-TO-DRAIN DIODE

NOTE: DUT is Shown as an N-Channel TMOS but can also be a P-Channel when appropriately connected. DUT Driver is the same device as DUT Diode (or Complement for P-Channel DUT Diode)

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and & are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.