# M-MOS Semiconductor Hong Kong Limited

### **8V Dual P-Channel Enhancement-Mode MOSFET**

$V_{DS} = -8V$

$\mathsf{R}_{\mathsf{DS}(\mathsf{ON})},\,\mathsf{V}_{\mathsf{gs}}@\text{-4.5V},\,\mathsf{I}_{\mathsf{ds}}@\text{-5.0A}=30m\,\Omega$

$R_{DS(ON)}$ ,  $V_{gs}$ @-2.5V,  $I_{ds}$ @-4.0A = 45m  $\Omega$

$R_{DS(ON)}$ ,  $V_{gs}$ @-1.8V,  $I_{ds}$ @-3.0A = 70m  $\Omega$

### **Features**

Advanced trench process technology

High Density Cell Design For Ultra Low On-Resistance

Ideal for battery multiplexing applications

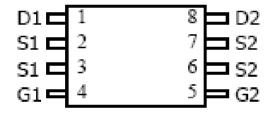

TSSOP-8

**Top View**

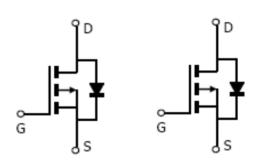

#### **Internal Schematic Diagram**

**P-Channel MOSFET**

#### **Maximum Ratings and Thermal Characteristics** ( $T_A = 25^{\circ}$ C unless otherwise noted)

|                                                         | ,                  |                                   | •          |      |  |

|---------------------------------------------------------|--------------------|-----------------------------------|------------|------|--|

| Parameter                                               | Symbol             | Limit                             | Unit       |      |  |

| Drain-Source Voltage                                    | V <sub>DS</sub> -8 |                                   |            |      |  |

| Gate-Source Voltage                                     | V <sub>GS</sub>    | ± 8                               | V          |      |  |

| Continuous Drain Current                                |                    | I <sub>D</sub>                    | -5         | ^    |  |

| Pulsed Drain Current 1)                                 |                    | I <sub>DM</sub>                   | -30        | A    |  |

| Maximum Power Dissipation                               | TA = 25°C          | В                                 | 1.1        | W    |  |

|                                                         | TA = 75°C          | - P <sub>D</sub>                  | 0.72       |      |  |

| Operating Junction and Storage Temperature Range        |                    | T <sub>J</sub> , T <sub>stg</sub> | -55 to 150 | °C   |  |

| Junction-to-Ambient Thermal Resistance (PCB mounted) 2) |                    | $R_{	hetaJA}$                     | 62.5       | °C/W |  |

Note: 1. Repetitive Rating: Pulse width limited by the maximum junction temperature

V 1.0

<sup>2. 1-</sup>in<sup>2</sup> 2oz Cu PCB board

# **Preliminary Data Sheet**

# **Dual P-Channel Enhancement-Mode MOSFET**

#### **ELECTRICAL CHARACTERISTICS**

| Parameter                        | Symbol              | Test Condition                                                                           | Min  | Тур  | Max  | Unit |

|----------------------------------|---------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| Static                           |                     |                                                                                          |      |      |      |      |

| Drain-Source Breakdown Voltage   | BV <sub>DSS</sub>   | $V_{GS} = 0V, I_D = 250uA$                                                               | -8   |      |      | V    |

| Drain-Source On-State Resistance | R <sub>DS(on)</sub> | $V_{GS} = -4.5V, I_D = -5.0A$                                                            |      | 24.0 | 30.0 | mΩ   |

| Drain-Source On-State Resistance | R <sub>DS(on)</sub> | $V_{GS} = -2.5V, I_D = -4.0A$                                                            |      | 33.0 | 45.0 |      |

| Drain-Source On-State Resistance | R <sub>DS(on)</sub> | $V_{GS} = -1.8V, I_D = -3.0A$                                                            |      | 48.0 | 70.0 |      |

| Gate Threshold Voltage           | $V_{GS(th)}$        | $V_{DS} = V_{GS}$ , $I_D = -250uA$                                                       | -0.4 | 0.6  | -1   | V    |

| Zero Gate Voltage Drain Current  | I <sub>DSS</sub>    | $V_{DS} = -8V$ , $V_{GS} = 0V$                                                           |      |      | -1   | uA   |

| Gate Body Leakage                | I <sub>GSS</sub>    | $V_{GS} = \pm 8V$ , $V_{DS} = 0V$                                                        |      |      | ±100 | nA   |

| Dynamic <sup>3)</sup>            |                     |                                                                                          |      |      |      |      |

| Total Gate Charge                | $Q_g$               | $V_{DS} = -6V, I_{D} = -5.0A$<br>$V_{GS} = -4.5V$                                        |      |      |      | nC   |

| Gate-Source Charge               | $Q_gs$              |                                                                                          |      |      |      |      |

| Gate-Drain Charge                | $Q_gd$              |                                                                                          |      |      |      |      |

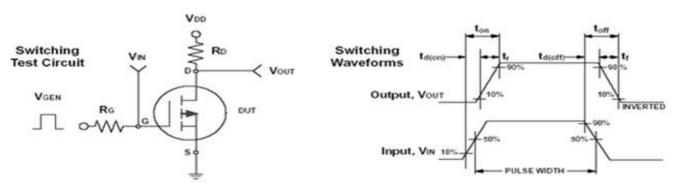

| Turn-On Delay Time               | t <sub>d(on)</sub>  | $V_{DD}$ = -6V, RL= $6\Omega$<br>$I_{D}$ = -1A, $V_{GEN}$ = -4.5V<br>$R_{G}$ = $6\Omega$ |      |      |      |      |

| Turn-On Rise Time                | t <sub>r</sub>      |                                                                                          |      |      |      | ns   |

| Turn-Off Delay Time              | t <sub>d(off)</sub> |                                                                                          |      |      |      |      |

| Turn-Off Fall Time               | t <sub>f</sub>      |                                                                                          |      |      |      |      |

| Input Capacitance                | C <sub>iss</sub>    | $V_{DS} = -6V, V_{GS} = 0V$<br>f = 1.0 MHz                                               |      |      |      | pF   |

| Output Capacitance               | C <sub>oss</sub>    |                                                                                          |      |      |      |      |

| Reverse Transfer Capacitance     | C <sub>rss</sub>    |                                                                                          |      |      |      |      |

| Source-Drain Diode               |                     |                                                                                          |      |      |      |      |

| Max. Diode Forward Current       | Is                  |                                                                                          |      |      |      | Α    |

| Diode Forward Voltage            | $V_{SD}$            | $I_S = -1.25A, V_{GS} = 0V$                                                              |      |      | -1.1 | V    |

Note: Pulse test: pulse width <= 300us, duty cycle<= 2%

<sup>3.</sup> Guaranteed by design; not subject to production testing

V 1.0

### **Notice**

- 1. Specification of the products displayed herein are subject to change without notice. Continuous development may necessitate changes in technical data without notice. M-MOS Semiconductor Sdn. Bhd. or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

- 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

V 1.0