Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No. : 1/6

### Advanced Schottky Barrier Diodes

# **ASD723S2**

#### Features:

- Low turn-on voltage

- Fast switching

- Pb-free lead plating and halogen-free package

#### Mechanical data:

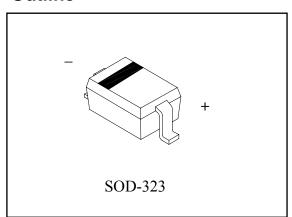

- Case: Molded Plastic, JEDEC SOD-323.

- Terminals: Pure tin plated, solderable per MIL-STD-750, method 2026.

- Polarity: Indicated by cathode band

- Mounting position: Any

- Weight: 4.8mg (approximately)

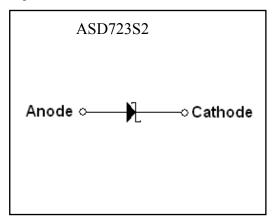

### **Symbol**

#### **Outline**

### **Ordering Information**

| Device          | Package                                                                                                                                                                           | Shipping                 |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| ASD723S2-0-T1-G | SOD-323 (Pb-free lead plating and halogen-free package)                                                                                                                           | 3000 pcs / tape & reel   |  |

|                 | Environment friendly grade: S for RoHS compliant products, or green compound products  Packing spec, T1: 3000 pcs / tape & reel, 7" reel  Product rank, zero for no rank products | G for RoHS compliant and |  |

| I               | Product name                                                                                                                                                                      |                          |  |

Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No. : 2/6

### **Absolute Maximum Ratings**(Ta=25°C)

| Characteristics                                                                              | Symbol            | Value       | Unit |

|----------------------------------------------------------------------------------------------|-------------------|-------------|------|

| Non-repetitive Peak Reverse Voltage                                                          | V <sub>RM</sub>   | 30          | V    |

| Forward Current                                                                              | IFM               | 200         | mA   |

| Forward Surge Current @ 8.3ms single half sine-wave superimposed on rated load(JEDEC method) | IFSM              | 1           | A    |

| Power dissipation @ Tc=25°C                                                                  | PD                | 250         | mW   |

| Thermal Resistance, Junction to ambient                                                      | R <sub>θ</sub> JA | 500         | °C/W |

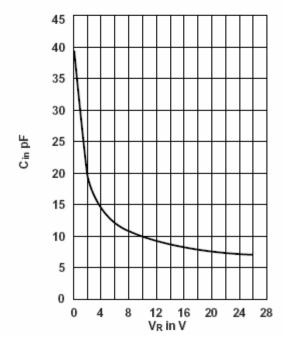

| Capacitance between Terminals @ f=1MHz and applied 10V <sub>DC</sub> Reverse Voltage         | Ст                | 15          | pF   |

| Operating Junction and Storage Temperature Range                                             | Tj, Tstg          | -65 to +150 | °C   |

### Electrical Characteristics (T<sub>A</sub>=25°C, unless otherwise noted)

| Parameter         | Condition             | Symbol         | Min | Тур | Max | Unit |

|-------------------|-----------------------|----------------|-----|-----|-----|------|

| Reverse Breakdown | I <sub>R</sub> =100μA | $V_R$          | 30  | _   | -   | V    |

| *Forward Voltage  | $I_F = 2mA$           |                | -   | 260 | -   | V    |

|                   | $I_F = 15 \text{mA}$  | <b>V</b> _     | -   | 320 | -   |      |

|                   | $I_F = 100 \text{mA}$ | V <sub>F</sub> | -   | 420 | -   | mV   |

|                   | $I_F = 200 \text{mA}$ |                | -   | 490 | 550 |      |

| Reverse Current   | $V_R = 30V$           | $I_R$          | -   | -   | 5   | μΑ   |

\*Pulse Test: Pulse Width  $\leq$ 380µs, Duty Cycle $\leq$ 2%

Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No. : 3/6

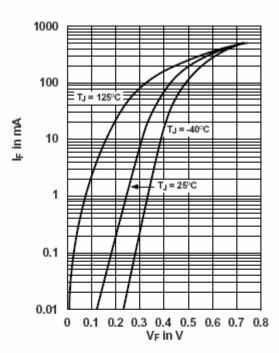

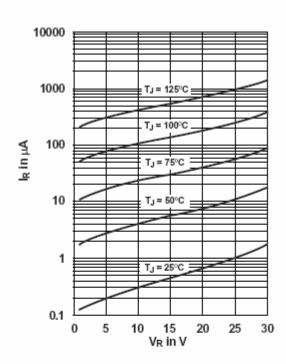

#### **Characteristic Curves**

Forward Voltage Forward Current at Various Temperatures (Typical Values)

Typical Capacitance °C vs. Reverse Applied Voltage VR

#### Typical Variation of Reverse Current at Various Temperatures

Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No. : 4/6

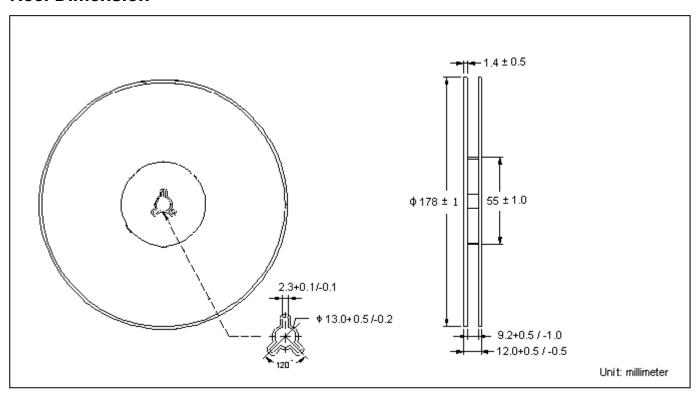

#### **Reel Dimension**

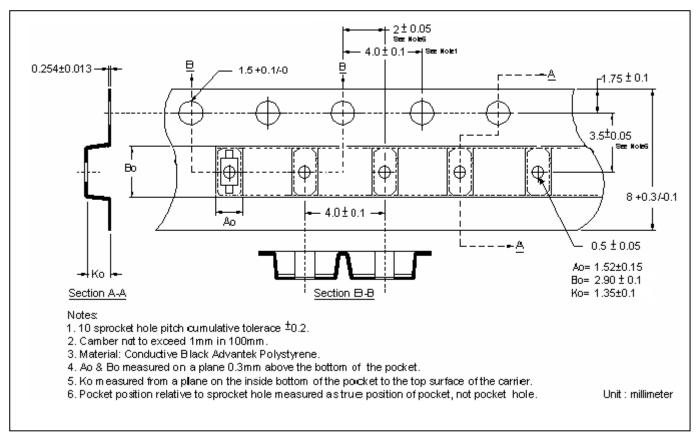

### **Carrier Tape Dimension**

Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No. : 5/6

Recommended wave soldering condition

| Product         | Peak Temperature | Soldering Time  |

|-----------------|------------------|-----------------|

| Pb-free devices | 260 +0/-5 °C     | 5 +1/-1 seconds |

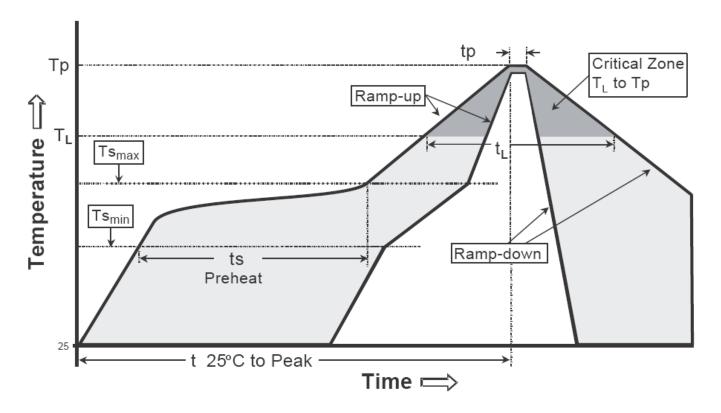

# Recommended temperature profile for IR reflow

| Profile feature                                                                                                     | Sn-Pb eutectic Assembly                 | Pb-free Assembly                        |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| Average ramp-up rate<br>(Tsmax to Tp)                                                                               | 3°C/second max.                         | 3°C/second max.                         |

| Preheat -Temperature Min(Ts min) -Temperature Max(Ts max) -Time(ts min to ts max)                                   | 100°C<br>150°C<br>60-120 seconds        | 150°C<br>200°C<br>60-180 seconds        |

| Time maintained above:  -Temperature (T <sub>L</sub> )  - Time (t <sub>L</sub> )  Peak Temperature(T <sub>P</sub> ) | 183°C<br>60-150 seconds<br>240 +0/-5 °C | 217°C<br>60-150 seconds<br>260 +0/-5 °C |

| Time within 5°C of actual peak temperature(tp)                                                                      | 10-30 seconds                           | 20-40 seconds                           |

| Ramp down rate                                                                                                      | 6°C/second max.                         | 6°C/second max.                         |

| Time 25 °C to peak temperature                                                                                      | 6 minutes max.                          | 8 minutes max.                          |

Note: All temperatures refer to topside of the package, measured on the package body surface.

Spec. No. : C343S2 Issued Date : 2009.03.17 Revised Date :2014.05.08

Page No.: 6/6

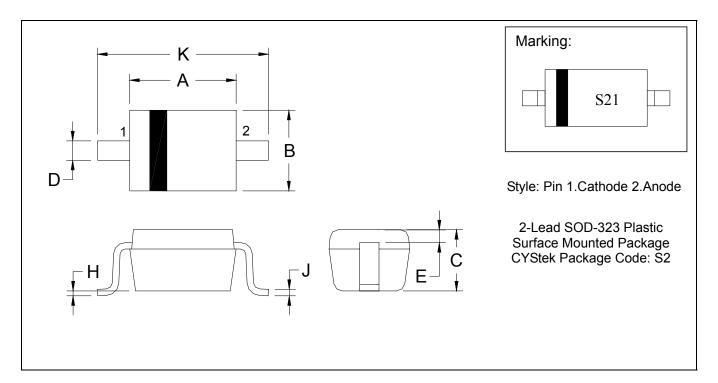

#### **SOD-323 Dimension**

#### \*: Typical

| DIM   | Inc    | hes    | Millim | eters | DIM   | Inc    | hes    | Millim | eters |

|-------|--------|--------|--------|-------|-------|--------|--------|--------|-------|

| DIIVI | Min.   | Max.   | Min.   | Max.  | ווועו | Min.   | Max.   | Min.   | Max.  |

| Α     | 0.0630 | 0.0709 | 1.60   | 1.80  | Е     | 0.0060 | -      | 0.15   | -     |

| В     | 0.0453 | 0.0531 | 1.15   | 1.35  | Н     | 0.0000 | 0.0040 | 0.00   | 0.10  |

| С     | 0.0315 | 0.0394 | 0.80   | 1.00  | J     | 0.0035 | 0.0070 | 0.089  | 0.177 |

| D     | 0.0098 | 0.0157 | 0.25   | 0.40  | K     | 0.0906 | 0.1063 | 2.30   | 2.70  |

Notes: 1.Controlling dimension : millimeters.

- 2.Lead thickness specified per L/F drawing with solder plating.

- 3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

#### Material:

- Lead: 42 Alloy ;pure tin plated

- Mold Compound: Epoxy resin family, flammability solid burning class: UL94V-0

#### Important Notice:

- All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of CYStek.

- CYStek reserves the right to make changes to its products without notice.

- CYStek semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.

- CYStek assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.